TSMC ha comunicato di aver avviato i primi test per la produzione di chip a 5 nm che, stando a quanto riferito, dovrebbero essere realizzati in massa entro giugno 2020.

Come spiegato durante la IEEE IEDM Conference, il nuovo processo produttivo a 5 nm (chiamato “N5”) utilizzerà la litografia ultravioletta estrema (EUV, Come nascono chip e processori ultraminiaturizzati con i sistemi EUV) in modo intensivo su 10 o più livelli. In questo modo, stando a quanto rivelano i portavoce di TSMC, si potranno realizzare chip di dimensione drasticamente ridotta rispetto agli attuali (40-45% di superficie in meno), con una potenza superiore del 15 % o capaci di ridurre del 30% i consumi energetici.

I risultati condivisi oggi da TSMC sono incoraggianti anche se – va detto – questi test iniziali non sono prodotti da destinare alla clientela.

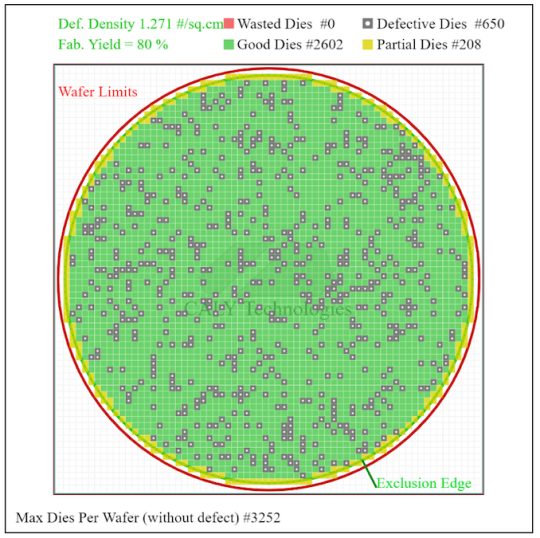

Inoltre, le prestazioni migliori si registrerebbero con la produzione dei SoC destinati agli smartphone (come nel caso degli Apple serie A o dei Qualcomm Snapdragon): in questo caso, infatti, l’azienda taiwanese riuscirebbe a estrarre l’80% di chip validi dal numero totale di chip prelevati dal wafer di silicio con il processo costruttivo a 5 nm.

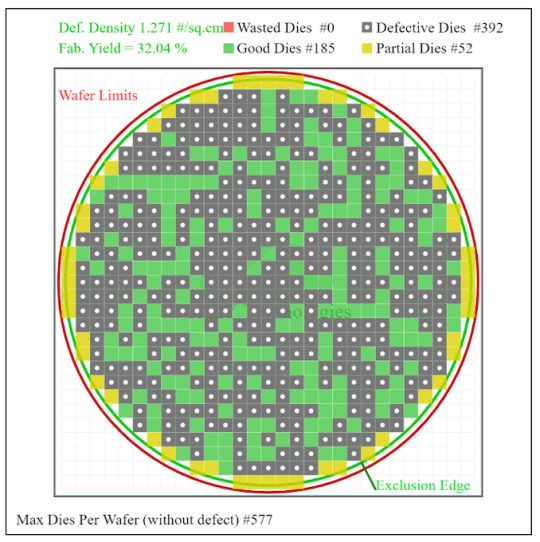

Meno incoraggianti i risultati ottenuti simulando la produzione di chip più grandi, come i processori destinati ad AMD. In questo caso TSMC avrebbe ottenuto solo il 32% di chip validi. La società conferma comunque che nei prossimi mesi migliorerà ulteriormente le tecniche produttive in modo tale da consegnare i primi chip a 5 nm ad AMD e agli altri partner intorno al 2021.

Suggeriamo la lettura degli articoli Perché i wafer di silicio sono sempre rotondi? e Nanometro, unità di misura utilizzata per descrivere le CPU: ecco perché per approfondire l’argomento.

/https://www.ilsoftware.it/app/uploads/2023/05/img_20411.jpg)

/https://www.ilsoftware.it/app/uploads/2025/04/SoC-intel-automotive.jpg)

/https://www.ilsoftware.it/app/uploads/2025/04/flux_image_476298_1745505623.jpeg)

/https://www.ilsoftware.it/app/uploads/2025/04/oneplus-13t.jpg)

/https://www.ilsoftware.it/app/uploads/2025/04/flux_image_476265_1745499891.jpeg)