NVidia ha annunciato la sua nuova e peraltro attesissima architettura Hopper, denominazione che vuole essere un omaggio alla pioniera della programmazione informatica Grace Murray Hopper: primo a utilizzarla sarà il chip GH100 anche se l’impiego sarà subito esteso ad altri prodotti che sono stati menzionati nella presentazione di oggi.

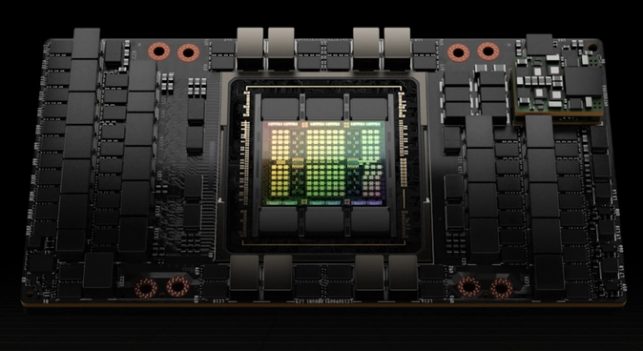

Il chip GH100 sarà principalmente il cuore pulsante dell’acceleratore H100 che sarà reso disponibile sia nel formato SXM5 che con interfaccia PCIe 5.

Il modello disponibile come scheda SXM5 è il più potente e consuma 700W; la versione PCIe si attesta sui 350W anche se in realtà sembra perdere solo il 20% di prestazioni rispetto al fratello maggiore. La larghezza di banda della memoria – ben 80 GB HBM3 a 4,8 Gbps – si riduce però da 3 a 2 TB/s.

H100 offre prestazioni da tre a sei volte superiori rispetto all’acceleratore A100 basato su architettura Ampere.

La potenza di calcolo dell’H100 SXM è di 60 TeraFLOPS in FP32 mentre la versione PCIe si ferma a 48 TeraFLOPS. Prestazioni ancora più incisive sono state fatte registrare, sempre secondo NVidia, usando formati di calcolo ampiamente utilizzati nell’intelligenza artificiale.

Il chip GH100, realizzato da TSMC a 4 nm e con una superficie pari a 814 mm2, utilizza ben 18.432 core CUDA e presenta fino a 576 core tensor con 60 MB di cache L2 e sei chip HBM3 con dodici controller a 512 bit che consentono di gestire fino a 96 GB di VRAM.

I core tensor utilizzano motori innovativi che si occupano dell’elaborazione dei modelli di apprendimento automatico. I vantaggi risulteranno tangibili nel computing basato sul linguaggio naturale e nelle applicazioni di visione artificiale (computer vision).

Con Hopper l’azienda di Santa Clara ha introdotto le istruzioni DPX per la programmazione dinamica. L’obiettivo è quello di suddividere un problema in sottoproblemi che possono essere risolti in modo ottimale; l’insieme delle soluzioni permette di risolvere il problema principale. Grazie al forte parallelismo delle GPU diventa possibile risolvere problemi molto complessi in modo efficace ed efficiente attraverso la ricorsione.

Le istruzioni DPX consentono di sgravare CPU e FPGA che di solito gestiscono le elaborazioni citate rendendo Hopper un’architettura più appetibile per le aziende.

Quali casi d’uso ha citato NVidia? L’analisi del genoma, l’ottimizzazione del routing di rete, l’analisi dei grafici e l’elaborazione di dati di vario tipo.

“Venti GPU H100 possono sostenere l’equivalente dell’intero traffico Internet mondiale rendendo possibile la realizzazione di sistemi avanzati ed efficaci modelli linguistici che eseguono inferenze sui dati in tempo reale“, ha dichiarato NVidia.

Le connessioni sulle schede H100 possono essere SXM con NVLink 4, il che aumenta la velocità a 900 GB/s rispetto ai 600 GB/s di NVLink 3. La connessione PCIe 5.0 sarà ovviamente un po’ un collo di bottiglia dal punto di vista prestazionale, soprattutto nel caso in cui si volessero abbinare più schede.

Ovviamente H100 non sarà per “i comuni mortali” visti anche i costi proibitivi per soggetti che non siano grandi aziende e istituti di ricerca di fama mondiale. Il chip sarà comunque utilizzabile sotto forma di macchina virtuale per i calcoli più intensivi selezionandolo tra i chip proposti dai principali fornitori di servizi cloud.

NVidia ha presentato anche il suo Grace Superchip basato su una coppia di chip Grace collegati utilizzando NVLink-C2C per l’interconnessione chip-to-chip. Il superchip consta di ben 144 core ARM che funzionano su un singolo socket, memoria LPDDR5x con ECC e potenza pari a 500W.

/https://www.ilsoftware.it/app/uploads/2023/05/img_24296.jpg)

/https://www.ilsoftware.it/app/uploads/2023/06/OpenAI-Logo-GPT-ChatGPT-IA-min.jpg)

/https://www.ilsoftware.it/app/uploads/2025/04/flux_image_475760_1744976324.jpeg)

/https://www.ilsoftware.it/app/uploads/2024/07/chip-IA-openai.jpg)

/https://www.ilsoftware.it/app/uploads/2025/04/grok-lg-ai-emotiva-pubblicita.jpg)