/https://www.ilsoftware.it/app/uploads/2023/05/img_18484.jpg)

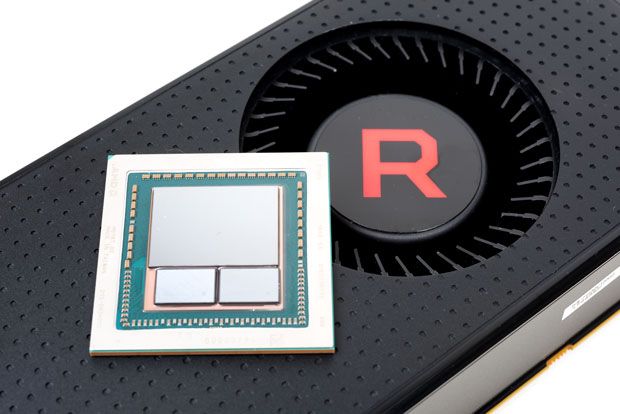

Le memorie HBM (High Bandwidth Memory) non hanno riscosso il successo che AMD si aspettava quando la società di Sunnyvale ha collaborato con Samsung e SK Hynix per il loro sviluppo.

Solo un ristretto numero di dispositivi utilizza oggi memorie HBM tra cui le schede video basate su architettura Vega e i processori Intel Kaby Lake G. Il motivo è essenzialmente legato ai costi: le memorie GDDR hanno infatti proseguito il loro processo evolutivo e le nuove GDDR6 offrono prestazioni davvero interessanti (fino a 20 Gbps nei modelli più evoluti) a costi inferiori (ne abbiamo parlato nell’articolo Scheda video, come sceglierla con una breve guida alle sue caratteristiche).

Lo JEDEC, organismo di standardizzazione dei semiconduttori che vanta oltre 300 membri, ha tuttavia approvato una revisione di HBM per venire incontro alle esigenze dei produttori e dare maggiore impulso alla diffusione di questo tipo di memorie.

I chip di memoria sono creati impilando uno sull’altro più layer: JEDEC ha standardizzato il numero di livelli utilizzabili per produrre memorie HBM, fino a 12. Una scelta che consentirà di realizzare memorie più capienti e di dimensioni minori riducendo allo stesso tempo i costi di produzione.

Le interconnessioni saranno realizzate usando l’integrazione TSV (Through-Silicon-Vias) ovvero condotti verticali inseriti nel wafer di silicio, riempiti con materiale conduttore che consente appunto le comunicazioni tra i circuiti integrati disposti verticalmente l’uno sull’altro.

A seconda delle caratteristiche di ciascun layer si potranno quindi avere fino a 24 GB di capacità per singolo chip di memoria.

Migliorata anche la velocità di comunicazione che giunge, secondo quanto ufficialmente stabilito dal JEDEC, a 2,4 Gbps per pin. Ciò significa che nei chip basati su bus a 1024 bit si potranno muovere 307 GB/s di dati. In un’unità grafica Vega dotata di due chip, la banda massima diverrebbe di 614 GB/s; un bel balzo in avanti rispetto agli attuali 484 GB/s.

/https://www.ilsoftware.it/app/uploads/2024/12/smart-glasses-scaled-scaled-1-224x120.webp)

/https://www.ilsoftware.it/app/uploads/2025/02/AWS-ocelot-chip-quantistico.jpg)

/https://www.ilsoftware.it/app/uploads/2025/02/jim-keller-AheadComputing-RISC-V.jpg)

/https://www.ilsoftware.it/app/uploads/2025/02/novita-SSD-samsung-9100-PRO.jpg)