Ispirandosi alla soluzione utilizzata da AMD per i suoi EPYC, Intel si starebbe preparando per lanciare sul mercato un processore Xeon destinato ai sistemi server basato su più chip interconnessi.

Al momento l’unico caso conosciuto di processori multichip realizzati in casa Intel è rappresentato dalle GPU Xe HP mentre ancora la società di Santa Clara non ha svelato alcuna CPU.

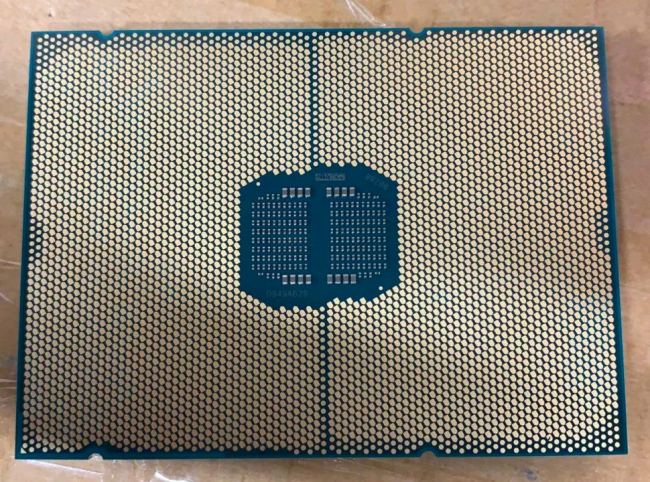

Tutto potrebbe cambiare con i primi esemplari di processori Xeon basati sull’utilizzo di chiplet: l’informazione questa volta non proviene da Intel ma da fonti vicine alla società che hanno pubblicato in anteprima le prime immagini delle CPU Sapphire Rapids delle quali avevamo parlato a suo tempo (Processori Intel e AMD per sistemi server: cosa cambierà da qui al 2022).

Fonte dell’immagine: ServeTheHome Forums.

Ciò che balza immediatamente agli occhi è l’utilizzo di due chip simmetrici anziché di uno solo monolitico.

Una soluzione simile a quella adottata da AMD? Non proprio. Perché gli ingegneri di AMD hanno scelto di separare completamente Northbridge e Southbridge mentre la CPU multicore con le cache sono su chip diversi. Quello che sembra un prototipo di pre-produzione Intel, invece, è appunto composto da due chip simmetrici; una configurazione MCM che ricorda la versione dual-core del Pentium 4 (Pentium D).

Più grande è un chip, meno chip possono essere prodotti a partire da un singolo per wafer di silicio (la resa tende inoltre a diminuire perché aumentano gli esemplari che soffrono di difetti). Ecco quindi che per i processori complessi come gli AMD EPYC o gli Intel Xeon ha senso suddividerli in chip più piccoli per migliorare la resa produttività e ridurre i costi.

I Sapphire Rapids utilizzeranno core Golden Cove con il supporto integrato per le estensioni AMX, AVX512_BF16 e AVX512_VP2INTERSECT progettate per l’utilizzo in ambito data center. Le nuovi CPU Xeon si serviranno inoltre di un controller di memoria DDR5, bus PCIe 5.0 da 32 GT/s compatibile con il CXL 1.1 per migliorare la connettività tra la CPU e i diversi acceleratori. Gli Xeon MCM verrebbero prodotti ricorrendo al processo costruttivo SuperFin 10 nm di Intel.

/https://www.ilsoftware.it/app/uploads/2023/05/img_22271.jpg)

/https://www.ilsoftware.it/app/uploads/2025/04/Chip-AMD-EPYC-Venice.jpg)

/https://www.ilsoftware.it/app/uploads/2025/04/amd-epyc-9005-turin-ubuntu-linux-prestazioni.jpg)

/https://www.ilsoftware.it/app/uploads/2025/04/chip-tenstorrent-blackhole.jpg)

/https://www.ilsoftware.it/app/uploads/2025/04/accordo-intel-tsmc.jpg)