Dopo essersi dedicato a “smontare” lo storico processore 8086, l’esperto Ken Shirriff – noto per le sue meticolose attività di reverse engineering sui chip che hanno fatto la storia dell’informatica – si è dedicato a dissezionare l’Intel 386, CPU che la società di Santa Clara ha presentato nel lontano 1985.

Il processore Intel 386 rappresenta un punto di svolta cruciale nell’evoluzione dei calcolatori moderni. A prima vista, potrebbe sembrare solo un “antenato” nella famiglia x86, ma il 386 ha giocato un ruolo determinante in diversi aspetti chiave dell’informatica del XX secolo.

Intel 386 fatto a pezzi

Un chip come l’Intel 386 (il suo nome completo è Intel 80386) ha segnato il passaggio all’architettura a 32 bit, stabilendo un nuovo standard di fatto che avrebbe dominato il panorama informatico per decenni. La sua introduzione ha anche sancito l’importanza dell’architettura x86 non solo per Intel ma per l’intera industria dei computer. Un cambiamento significativo, poiché ha decretato la fine del monopolio di IBM sul mercato dei PC, aprendo la strada a nuovi leader come Compaq.

Shirriff mostra le caratteristiche salienti del processore Intel 386, focalizzandosi sulle sue evoluzioni e sulle scoperte chiave che emergono dall’analisi del die di silicio. Uno sguardo ravvicinato alle foto del die rivela modifiche sostanziali nella transizione dalla tecnologia a 1,5 µm a quella a 1 µm. Questa riduzione dimensionale del 60% ha comportato non solo una maggiore densità a livello di transistor ma anche significative modifiche nel layout del processore. Il passaggio da 1.5 µm a 1 µm potrebbe sembrare un dettaglio tecnico trascurabile, ma ha avuto un impatto significativo, abbassando i costi di produzione. Questa strategia di ridimensionamento del processore prima del successivo passaggio a una nuova microarchitettura si è concretizzata nella cosiddetta strategia tick-tock di Intel.

Durante la fase tick, Intel introduce una nuova tecnologia di processo più avanzata. Gli ingegneri si focalizzano sull’aggiornamento della tecnologia di fabbricazione dei chip, riducendo le dimensioni dei transistor e migliorando l’efficienza energetica. Tuttavia, l’architettura del processore tende a rimanere in gran parte invariata rispetto alla generazione precedente.

Nella fase tock, Intel introduce un’architettura completamente nuova o sostanzialmente rivista, mantenendo la stessa tecnologia di processo di produzione della fase “tick”. In questa fase, l’attenzione è rivolta a miglioramenti significativi delle prestazioni, nuove istruzioni e funzionalità, oltre a un design del processore più avanzato.

Le firme dei progettisti che hanno curato il design di Intel 386

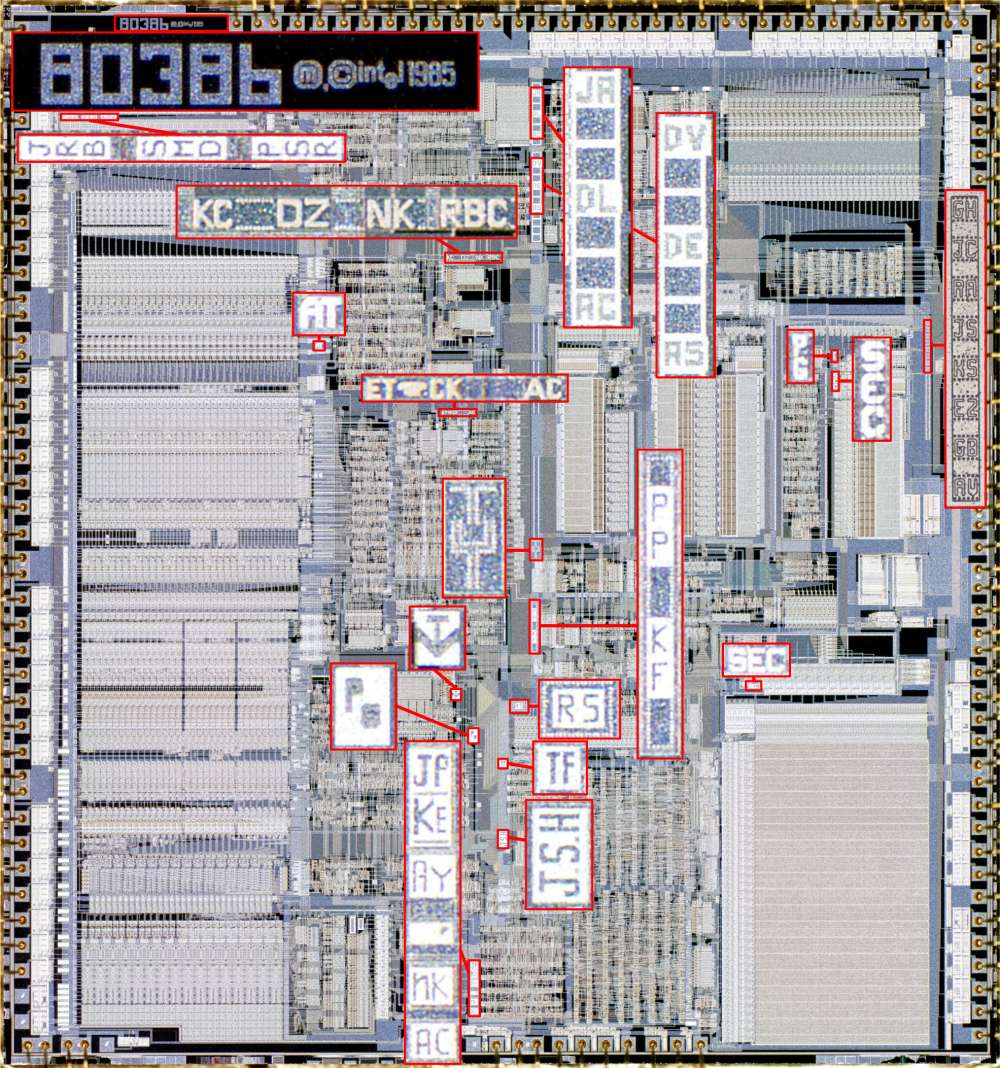

Shirriff mette particolarmente in risalto la scoperta delle firme dei progettisti che hanno curato lo sviluppo del processore Intel 386. È infatti consuetudine che i die in silicio riportino le iniziali degli ingegneri che hanno lavorato sul progetto. L’esperto, tuttavia, fa notare che sul processore 386 DX figura un numero insolitamente elevato di iniziali. “Penso che i progettisti abbiano messo le loro iniziali accanto all’unità su cui hanno lavorato, ma non sono riuscito a identificare la maggior parte dei nomi“, aggiunge Shirriff.

Il die del processore Intel 386 con le iniziali dei progettisti ingrandite. Fonte: Examining the silicon dies of the Intel 386 processor.

Il 386 originale era costruito su un processo chiamato CHMOS-III a 1,5 µm (tale misura coincideva, in particolare, con la lunghezza del canale di gate per ciascun transistor). Intorno al 1987, Intel passò a un processo migliorato chiamato CHMOS-IV, con caratteristiche da 1 µm, consentendo la realizzazione di un die considerevolmente più piccolo per il processore 386.

Curiosamente, nel passaggio a 1 µm molte delle iniziali dei progettisti sono state rimosse, aggiungendo un elemento intrigante alla storia del design del chip Intel.

La progettazione del chip Intel 386

Il processo di progettazione dell’Intel 386 si è rivelato un percorso interessante che ha decretato la transizione verso l’uso di sistemi di progettazione automatizzati e una maggiore utilizzo della simulazione. In quel periodo, i responsabili dell’azienda si resero conto che sarebbe stata necessaria una maggiore automazione per costruire un chip complesso come il 386 nei tempi previsti.

Facendo un grande investimento in strumenti automatizzati, il team 386 completò la progettazione in anticipo rispetto alla tabella di marcia. Oltre agli strumenti CAD proprietari, il team fece largo uso di software Unix standard come sed, awk, grep e make per gestire i vari database di progettazione.

Il 386 pose nuove sfide di progettazione rispetto al processore precedente, il 286. Era molto più complesso, con il doppio dei transistor; utilizzava anche circuiti fondamentalmente diversi. Mentre i processori precedenti erano costruiti con transistor NMOS, il 386 passò a CMOS (la tecnologia ancora in uso oggi). Il processo CHMOS citato in precedenza, prevedeva due strati di metallo anziché uno, cambiando il modo in cui i segnali venivano instradati sul chip e richiedendo nuove tecniche di progettazione.

Il problema del forbidden gap

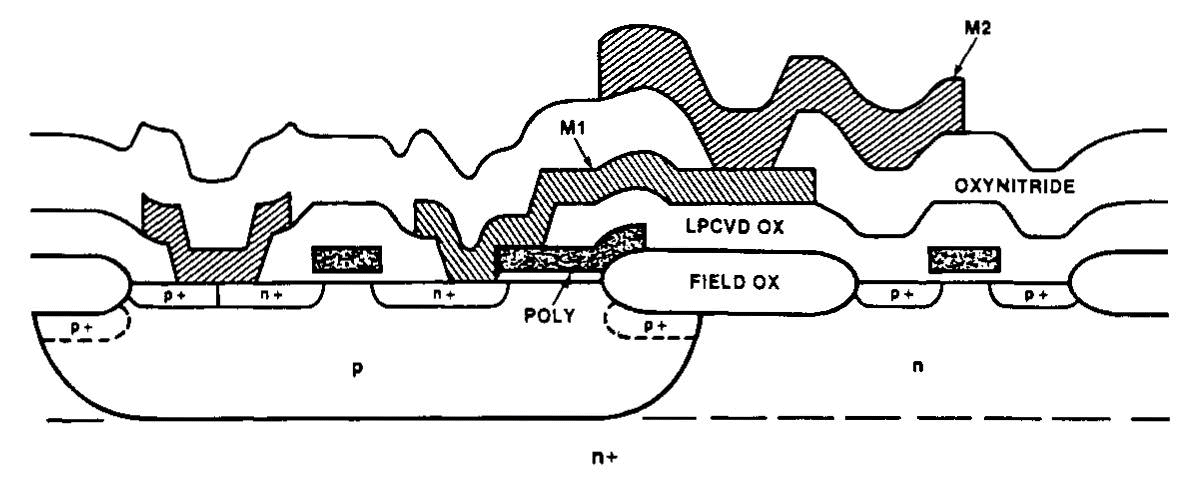

Nella sua dettagliata analisi, Shirriff racconta il problema del forbidden gap che Intel ha dovuto affrontare durante la progettazione del suo 386. Forbidden gap è una regione critica in cui la disposizione degli strati metallici sul silicio può causare problemi. Nel caso specifico del CHMOS-III, lo strato superiore in metallo poteva attraversare o avvicinarsi allo strato inferiore. Intel dovette però affrontare il problema in cui i filamenti metallici andavano a toccarsi provocando un malfunzionamento del chip, che rendeva il prodotto non affidabile.

Fonte: A double layer metal CHMOS III technology.

La necessità di gestire questa problematica ha richiesto un approccio attento alla disposizione degli strati metallici e alle distanze tra di essi durante il processo di progettazione e fabbricazione del chip. Questa complicazione aggiuntiva ha influenzato la resa complessiva del 386 e ha richiesto soluzioni innovative per garantire che il chip funzionasse correttamente. Il diagramma mostra una sezione trasversale di un circuito CHMOS-III, con un transistor NMOS a sinistra e un transistor PMOS a destra.

Progettazione mista top-down e bottom-up

La progettazione del 386 procedette sia con un approccio top-down, iniziando con la definizione dell’architettura, sia dal bootom-up, progettando celle standard e altri circuiti di base a livello di transistor. Il microcodice del processore, il software che controllava il chip, era un componente fondamentale. Fu progettato con due strumenti CAD: un assembler e un microcode rule checker.

Il design ad alto livello del chip (register-level RTL) fu creato e affinato fino a rappresentare i tempi di clock e le fasi temporali in modo dettagliato.

Register-level RTL si riferisce a una descrizione a livello di registro (Register Transfer Level) durante la progettazione di un processore o di un circuito integrato. È una descrizione che si concentra sul modo in cui i dati vengono trasferiti tra i registri durante l’esecuzione di istruzioni da parte del processore. Si tratta di un passo intermedio durante la progettazione di un processore, situato tra la progettazione ad alto livello, che riguarda l’architettura complessiva del processore, e la progettazione a livello di gate, che coinvolge la descrizione dettagliata a livello di transistor dei singoli componenti del processore.

Il RTL fu programmato in MAINSAIL, un linguaggio portabile simile ad Algol basato su SAIL (Stanford Artificial Intelligence Language). Intel utilizzò un simulatore proprietario chiamato Microsim per simulare RTL.

Il diagramma del processore Intel 386 alto 5 metri

Utilizzando come fonte la relazione annuale Intel del 1985, Shirriff ha ricomposto anche la storica immagine riprodotta nella figura di seguito. Essa rappresenta un diagramma del processore 386, alto nella realtà ben 5 metri, che corrisponde a una rappresentazione visiva del processore molto dettagliata e ingrandita. Lo schema descrive la disposizione dei componenti principali del processore: il datapath che include registri, ALU (Arithmetic Logic Unit), barrel shifter e unità di moltiplicazione/divisione, è posizionato a sinistra. Il microcodice, che rappresenta le istruzioni di basso livello che controllano il funzionamento del processore, è posizionato nell’angolo in basso a destra.

Shirriff confessa che data la complessità e l’aspetto artistico del diagramma, è difficile stabilire se si tratta di un lavoro creato a fini ingegneristici o se sia un’opera d’arte degna di essere esposta, ad esempio, al Museum of Modern Art (MoMA) di New York.

Nell’immagine in apertura (fonte: Intel) il secondo a partire da destra è un giovane Pat Gelsinger, oggi CEO dell’azienda, che rivestì un ruolo chiave nello sviluppo del processore 80386.

/https://www.ilsoftware.it/app/uploads/2023/10/intel-386-intro-storia.jpg)

/https://www.ilsoftware.it/app/uploads/2025/04/intel-18a-dettagli-tecnici.jpg)

/https://www.ilsoftware.it/app/uploads/2025/04/Chip-AMD-EPYC-Venice.jpg)

/https://www.ilsoftware.it/app/uploads/2025/04/amd-epyc-9005-turin-ubuntu-linux-prestazioni.jpg)

/https://www.ilsoftware.it/app/uploads/2025/04/chip-tenstorrent-blackhole.jpg)