/https://www.ilsoftware.it/app/uploads/2023/09/DRAM-memoria-3D-XRAM.jpg)

La tecnologia alla base del funzionamento delle memorie DRAM (Dynamic Random Access Memory) è in costante evoluzione. L’obiettivo è quello di aumentare la densità e migliorare le prestazioni. Numerose aziende e istituti di ricerca sono costantemente al lavoro su soluzioni “inedite” per aprire la porta alla diffusione in ambito commerciale di soluzioni tecnologiche innovative.

Una delle principali metodologie per aumentare la densità, consiste nell’impilamento di più strati di celle di memoria. Questo approccio consente di aumentare le capacità senza accrescere le dimensioni fisiche del chip: lo abbiamo visto con lo storage basato su memorie flash NAND 3D; lo iniziamo a vedere adesso con le DRAM 3D.

Cosa significa aumentare la densità delle DRAM

Aumentare la densità delle DRAM significa accrescere la quantità di dati che un singolo chip di memoria può gestire. Diverse tecniche possono contribuire ad aumentare la densità delle DRAM, tra cui il già citato impilamento dei chip di memoria, l’utilizzo di tecnologie di produzione più avanzate e l’adozione di nuove architetture di memoria.

L’uso di processi di fabbricazione più avanzati, come l’adozione della litografia estrema ultravioletta (EUV), ha permesso di progettare e realizzare chip con caratteristiche sempre più miniaturizzate. Le architetture di memoria avanzate, più efficienti e intelligenti, presuppongono l’utilizzo di tecniche di compressione dei dati, la progettazione di schemi di indirizzamento più efficienti e l’implementazione di algoritmi avanzati.

L’adozione di materiali evoluti per le celle di memoria può, essa stessa, contribuire a migliorare la densità delle DRAM: l’uso di materiali con proprietà dielettriche superiori può ad esempio consentire la riduzione delle dimensioni.

Alcune nuove proposte coinvolgono l’utilizzo di soluzioni per la memorizzazione dei dati che si allontanano dalla natura intrinsecamente volatile delle DRAM (si pensi alle memorie UltraRAM) e, infine, si guarda ai progressi dell’informatica quantistica e del quantum computing per rivoluzionare l’approccio all’archiviazione delle informazioni.

Cos’è il problema della scalabilità delle DRAM

Il concetto di scalabilità delle DRAM si riferisce alla capacità di aumentare la densità di memorizzazione e le prestazioni delle memorie in modo efficace e sostenibile nel tempo. Tuttavia, le dimensioni fisiche delle celle di memoria continuano a rappresentare un problema di fondo: ridurre le dimensioni delle celle, infatti, può comportare problemi di integrità dei dati elettrici (ad esempio, perdita di carica).

Inoltre, aumentare la densità delle DRAM richiede spesso una maggiore quantità di energia per gestire le operazioni di lettura e scrittura, il che può portare a problemi di dissipazione del calore e consumo di energia eccessivo.

I design dei circuiti DRAM attuali richiedono essenzialmente tre componenti: una bitline (una struttura conduttiva che inietta corrente); un transistor che riceve la corrente in uscita dalla bitline e funge da gate (quest’ultimo controlla se la corrente elettrica può fluire nel circuito); un condensatore in cui la corrente che passa attraverso la bitline e il transistor viene infine memorizzata sotto forma di bit (0 o 1). Abbiamo visto cos’è il codice binario.

La soluzione di Lam Research

Nelle settimane scorse, Lam Research, azienda con sede a Fremont (California), specializzata nella progettazione di circuiti basati su semiconduttori, ha pubblicato una proposta su come potrebbero evolvere le future DRAM.

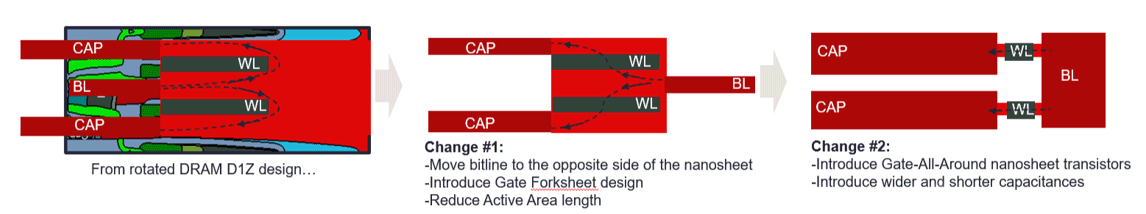

Utilizzando il loro software proprietario SEMulator3D, gli esperti di Lam Research hanno presentato vari possibili design di memorie DRAM 3D. Il principale obiettivo era quello di affrontare proprio le sfide legate alla scalabilità e all’impilamento degli strati. Spostare in tre dimensioni quanto fatto “fino a ieri” in 2D significa dover gestire accuratamente i problemi relativi alla dissipazione del calore e alle interconnessione tra gli strati.

Gli sforzi si sono inoltre concentrati sulla riduzione delle dimensioni dei condensatori e dei transistor all’interno delle celle di memoria DRAM.

Fonte dell’immagine: 3D DRAM Is Coming. Here’s a Possible Way to Build It.

I ricercatori hanno studiato l’impiego dei cosiddetti array di via come il TSV (Through Silicon Vias) di TSMC: si tratta di strutture che consentono la connessione verticale tra strati diversi all’interno di un chip. Ancora una volta, il fine è quello di collegare gli strati che formano le DRAM 3D in modo efficiente.

Lam Research ha infine stabilito i requisiti di processo necessari per fabbricare il design proposto. Questo ha comportato la definizione dei parametri e delle specifiche da rispettare per realizzare con successo il design di DRAM 3D.

Le soluzioni adottate da Lam Research in fase di progettazione

Alcuni “trucchi” di progettazione hanno visto lo spostamento della bitline sul lato opposto del transistor: poiché la bitline non è più circondata dal condensatore, più transistor possono essere collegati direttamente alla bitline stessa, migliorando la densità del chip.

Fonte dell’immagine: 3D DRAM Is Coming. Here’s a Possible Way to Build It.

Per massimizzare i guadagni in termini di densità di area, Lam Research ha inoltre sfruttato alcune moderne tecniche di produzione dei transistor: tra queste gli esperti citano Forksheet Gate-All-Around (GAA), che Intel sembra stia utilizzando per sviluppare tecnologie di gating di prossima generazione. L’architettura DRAM proposta può essere impilata, con uno schema simile a quanto già avviene oggi con le memorie NAND.

Perché la soluzione usata nelle memorie NAND non si applica direttamente per le DRAM

Le NAND sono un tipo di memoria flash non volatile utilizzata per la memorizzazione permanente dei dati. A differenza delle memorie DRAM, che devono essere alimentate in continuazione per mantenere i dati, le NAND mantengono i dati anche quando non sono alimentate.

Sono soluzioni per la memorizzazione dei dati ampiamente sfruttate in un ampio ventaglio di dispositivi: unità SSD, chiavette USB, unità rimovibili, schede SD, smartphone e tablet. Le NAND, inoltre, sono costituite da una serie di righe e colonne che formano una griglia, alle cui intersezioni sono presenti le celle di memoria. Ogni cella di memoria può contenere uno o più bit di informazione, a seconda della densità di memoria del chip.

Mentre la scalabilità delle NAND è attualmente intorno a 232 strati, Lam Research stima che la prima generazione delle DRAM 3D basate su un design come quello proposto sfrutterebbe al massimo 28 strati impilati l’uno sull’altro. Le memorie DRAM sono progettate per l’accesso rapido ai dati e affrontano sfide tecniche significative nell’impilamento degli strati senza compromettere le prestazioni.

Ciò premesso, i tecnici sono convinti che tra 5-8 anni sia possibile realizzare davvero un esemplare di memoria DRAM 3D commerciale. Da lì in avanti inizierà un periodo di interregno quantificabile in circa 3 anni per la definitiva migrazione dalle attuali DRAM 2D alle versioni 3D.

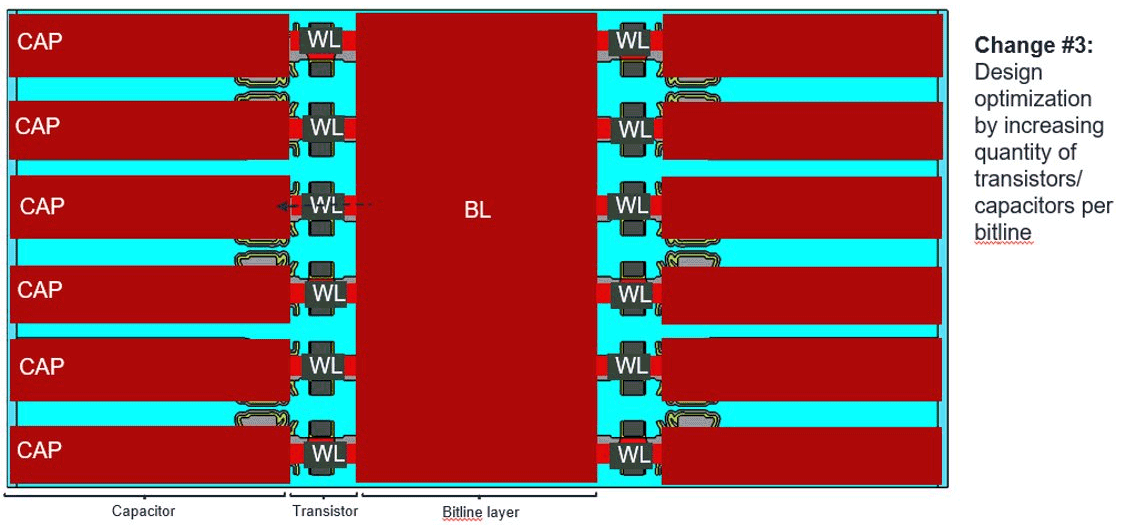

Le memorie 3D X-RAM di Neo Semiconductor

A maggio 2023, alcuni mesi prima rispetto allo studio di Lam Research, Neo Semiconductor ha presentato le sue memorie 3D X-DRAM. Se ne è poi continuato a parlare per tutta l’estate, con la pubblicazione ad agosto di una presentazione aggiornata.

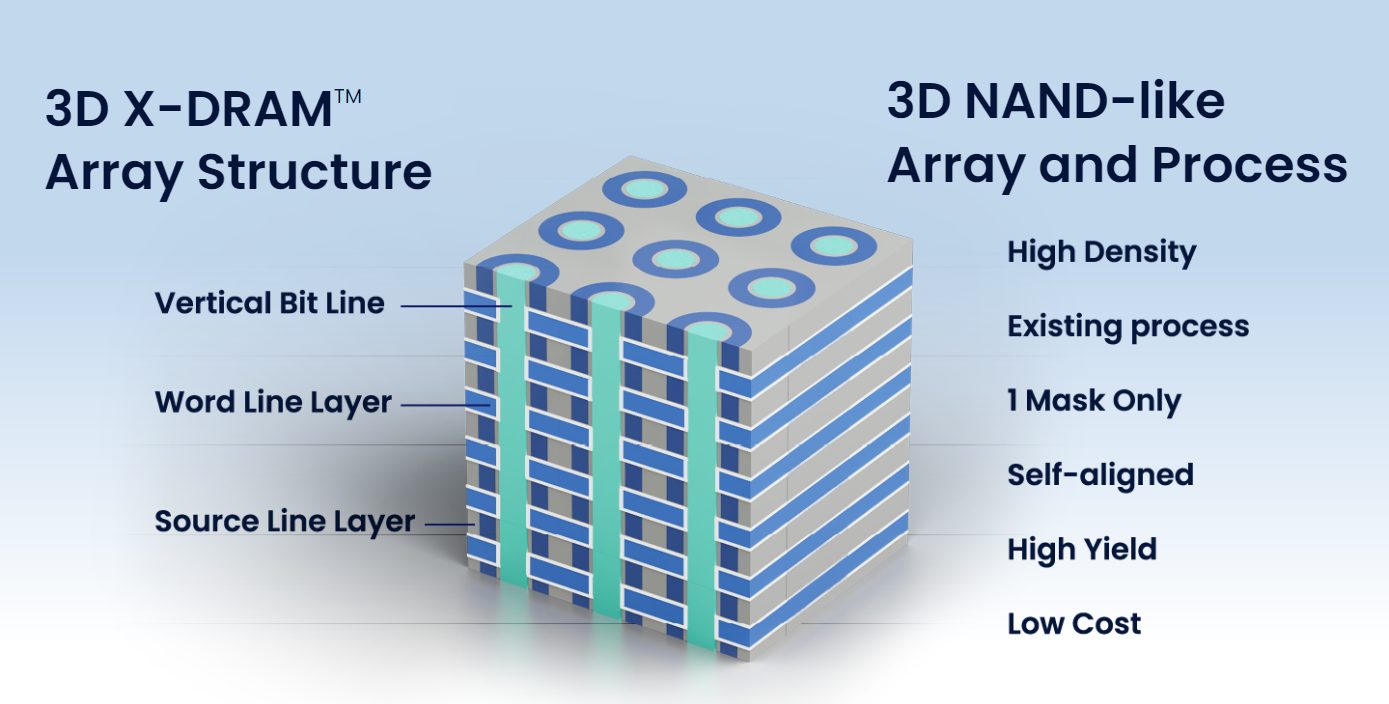

3D X-RAM è una soluzione che si serve della tecnologia Floating Body Cell (FBC) per immagazzinare i dati come cariche elettriche utilizzando un solo transistor e zero condensatori. Questa tecnologia di memoria è simile alla soluzione utilizzata per gli SSD NAND con chip a 230 strati e una densità di 128 Gb.

Fonte dell’immagine: Neo Semiconductor.

Le memorie 3D X-DRAM di Neo Semiconductor, azienda fondata nel 2012 a San Jose (California), sono progettate per portare la densità dei chip DRAM addirittura fino a 2 Terabyte, otto volte di più rispetto agli standard di oggi.

A differenza di molte alternative proposte nei documenti accademici e studiate dall’industria, l’adozione di 3D X-DRAM parte dall’utilizzo del processo 3D NAND attuale: in questo modo, a detta dei promotori della soluzione, si può sostenere in maniera adeguata la crescente domanda di memorie ad alta capacità e prestazioni guidata dalla prossima ondata di applicazioni di intelligenza artificiale.

Fonte dell’immagine: 3D X-RAM, World’s first 3D NAND-like DRAM, Neo Semiconductor, agosto 2023.

Credit immagine in apertura: iStock.com/yasindmrblk

/https://www.ilsoftware.it/app/uploads/2025/04/SoC-intel-automotive.jpg)

/https://www.ilsoftware.it/app/uploads/2025/04/flux_image_476298_1745505623.jpeg)

/https://www.ilsoftware.it/app/uploads/2025/04/oneplus-13t.jpg)

/https://www.ilsoftware.it/app/uploads/2025/04/flux_image_476265_1745499891.jpeg)