Le architetture ARM64 e x86-64 sono ampiamente utilizzate nell’industria dei computer, dell’elettronica e dei dispositivi mobili. ARM64, che sta per Advanced RISC Machine 64-bit, è basata su un set di istruzioni ridotto (RISC): si tratta di un’architettura ampiamente utilizzata nei dispositivi mobili come smartphone e tablet anche se sta da tempo guadagnando grande popolarità anche nel mercato dei server e nei data center. D’altra parte, x86-64 (altrimenti nota come AMD64 o Intel 64) è un’architettura basato su un set di istruzioni complesso (CISC).

Delle principali differenze tra processori ARM e x86 abbiamo già parlato in un altro articolo: quando si parla delle due piattaforme, tuttavia, si tende a concentrarsi sulle difformità in termini di ISA (Instruction Set Architecture). Sebbene si tratti di temi certamente importanti, come sottolineato a suo tempo dallo stesso Jim Keller in una bella intervista, focalizzarsi prevalentemente sul tema ISA è un po’ una perdita di tempo. Keller è il leggendario ingegnere che, tra i vari progetti ai quali si è dedicato nel corso della sua attività professionale, non è possibile non ricordare la progettazione dei processori Apple A4/A5 oltre che dell’architettura AMD Zen. Keller ha dichiarato che “litigare sui set di istruzioni è qualcosa di molto triste“.

ARM64 e x86-64: architetture a 64 bit

Il numero “64” che appare nelle denominazioni ARM64 e x86-64 indica la larghezza di ciascuna word utilizzata dal processore: suggerisce la dimensione dei registri interni e la dimensione massima dei dati che possono essere elaborati in un’unica istruzione. Ne parliamo nell’articolo su come funziona un processore.

Nel caso di ARM64, indica che l’architettura utilizza registri a 64 bit. I registri di 64 bit consentono di elaborare dati di dimensioni maggiori e di eseguire operazioni più complesse in un’unica istruzione. Questo porta a un miglioramento delle prestazioni e alla possibilità di gestire carichi di lavoro più impegnativi.

Nel caso di x86-64, il “64” indica la transizione dall’architettura x86 alla versione a 64 bit. L’architettura x86 originale era basata su registri a 32 bit; con l’introduzione di x86-64, l’architettura è stata estesa per supportare registri più ampi rispetto al passato. In un altro articolo spieghiamo perché x86 è feudo di Intel e AMD.

In generale, le piattaforme a 64 bit offrono una capacità di indirizzamento aumentata (vi ricordate della possibilità, con i processori x86-64 di usare sistemi dotati di oltre 4 GB di memoria RAM? Ne parliamo nell’articolo sulle differenze tra 32 e 64 bit), il supporto per l’elaborazione di dati di maggiori dimensioni, prestazioni migliorate (almeno in linea generale) perché si possono eseguire operazioni su dati di dimensioni maggiori in un singolo ciclo di clock. In alcuni casi molto specifici, l’esecuzione di codice ad esempio a 32 bit può risultare più performante rispetto ai 64 bit (dimensioni del codice ridotte, cache più efficiente, uso di processori a bassissimo consumo energetico).

In generale, però, la corsa 8, 16, 32, 64 bit ha portato a un significativo avanzamento, su ogni architettura, in termini di capacità di elaborazione dei dati e prestazioni complessive.

Cos’è un’ISA

Un’ISA è un insieme di istruzioni che un processore è in grado di comprendere ed eseguire. L’ISA definisce il set di operazioni di base che un processore può svolgere, nonché le modalità di accesso alla memoria, l’organizzazione dei registri, il formato stesso delle istruzioni e altre caratteristiche legate all’interazione tra il processore, il resto del sistema e il software.

Ciascuna ISA fornisce una specifica di alto livello che consente agli sviluppatori di creare software compatibile con una determinata architettura. I compilatori, per esempio, traducono il codice sorgente in istruzioni comprensibili dal processore basato su un’ISA specifica: in un altri articolo abbiamo visto le differenze tra compilatore e interprete.

Le architetture ISA possono variare notevolmente in base alle loro caratteristiche e ai loro obiettivi. Alcuni esempi comuni di ISA includono, oltre a x86 e ARM, anche MIPS, PowerPC, SPARC e RISC-V, quest’ultima sempre più di attualità e accreditata di essere l’architettura del futuro, soprattutto per via dell’esenzione da qualsiasi royalty.

L’ISA è di fondamentale importanza perché definisce l’interfaccia tra il software e l’hardware. Essa determina come il processore interpreta e esegue le istruzioni, come accede alla memoria, come manipola i dati e come interagisce con i dispositivi periferici.

Perché parlando di ARM e x86, l’ISA conta poco o nulla

Come abbiamo accennato in precedenza e nell’articolo correlato, originariamente i chip CISC miravano a eseguire meno istruzioni più complesse e a svolgere un quantitativo di lavoro più importante per ciascuna istruzione. RISC ha utilizzato istruzioni più semplici che sono più facili e veloci da eseguire. In sintesi, mentre l’architettura CISC mira a offrire istruzioni complesse e complete in un’unica operazione, l’architettura RISC si concentra su istruzioni più semplici ed efficienti, ottimizzate per l’esecuzione veloce e l’utilizzo efficiente dei cicli di clock.

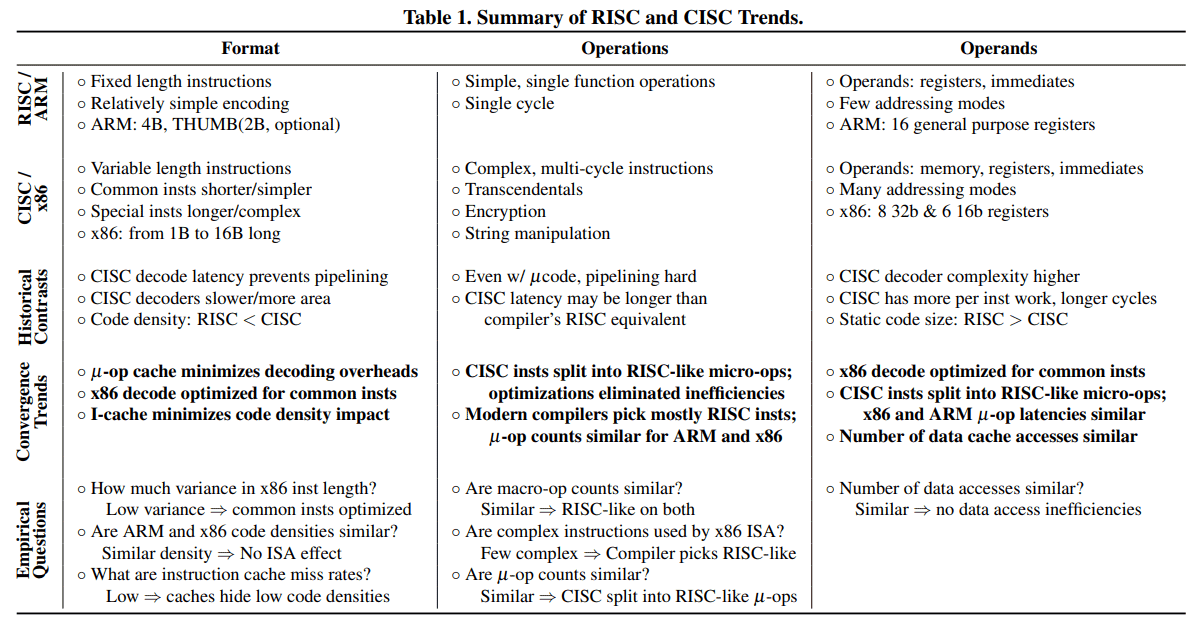

Una tabella elaborata dagli accademici dell’Università del Wisconsin (l’articolo è citato nel testo), mostra come le due architetture RISC/ARM e CISC/x86 tendano a convergere.

Tuttavia, fatta questa premessa, va detto che questa distinzione non esiste più e non ha senso di esistere. Lo conferma lo stesso Keller osservando che oggi, all’atto pratico, non c’è alcuna differenza significativa tra RISC/ARM e CISC/x86 per quanto riguarda le prestazioni. Ciò che conta è mantenere i core alimentati con i dati giusti e concentrarsi su questioni come la progettazione della cache, la previsione dei salti a livello di codice (branch prediction; se ne è parlato tanto nel caso degli attacchi side-channel), il precaricamento e una varietà di “tattiche” utili per prevedere se del codice può essere eseguito in anticipo.

Quanto sostenuto da Keller era già stato messo nero su bianco anche molto tempo prima, già nel 2013, in uno studio firmato da Emily Blem e da altri ricercatori. Nell’importante documento si può leggere come le CPU ARM e x86 differissero in termini di consumo energetico e prestazioni principalmente perché erano state ottimizzate con obiettivi diversi in mente. Il set di istruzioni ha poco valore su questi punti mentre a contare davvero tanto è il design della CPU. Le differenze in termini di ISA hanno implicazioni implementative, ma le moderne tecniche di microarchitettura le rendono discutibili: di fatto una certa ISA non è fondamentalmente più efficiente di un’altra.

Alcuni anni fa Linus Sebastian legava le ISA ARM e x86 alla potenza del chip: ciò non corrisponde al vero in quanto il design di ogni singolo processore è fortemente condizionato dal tipo di utilizzo che si andrà a fare di quel dispositivo.

Si legge spesso, inoltre, che ARM utilizza istruzioni di lunghezza fissa, mentre le istruzioni di x86 variano in lunghezza. Poiché è necessario determinare la lunghezza di un’istruzione prima di sapere dove inizia la successiva, decodificare le istruzioni x86 in parallelo è più difficile. Sulla carta questo è vero ma in pratica, come conferma lo stesso Keller, non si tratta di uno svantaggio per i processori x86 ad alte prestazioni.

Nel 2016, uno studio supportato dall’Helsinki Institute of Physics ha esaminato la microarchitettura Haswell di Intel per capire quando il meccanismo di decodifica delle istruzioni x86 incidesse sulle prestazioni globali del processore. Ebbene, il risultato è che il peso delle attività di decodifica è irrilevante, anche con i processori x86-64, e si perde nel “mare” di attività svolte dal chip. Ogni watt, però, è importante quando un processore deve lavorare su un sistema limitato dal punto di vista energetico. D’altra parte, va detto che anche le operazioni di decodifica su ARM hanno un costo: proprio come le CPU x86, anche i core ARM utilizzano cache operative (op cache) per ridurre i costi di decodifica. Il “vantaggio di decodifica” di ARM non è abbastanza importante da consentire ad ARM di evitare l’uso di op cache progettate per memorizzare le istruzioni più frequentemente utilizzate, in modo da accelerare l’esecuzione del codice e ridurre i tempi di accesso alla memoria principale.

Va detto, inoltre, che le moderne CPU ARM decodificano inoltre le istruzioni ARM in più micro-operazioni: quando l’istruzione viene eseguita, essa è dapprima decodificata e suddivisa in una sequenza di micro-ops, che sono le operazioni elementari eseguite dal processore. Esse consentono al processore di lavorare su unità di lavoro più piccole, eseguire operazioni in parallelo e applicare diverse ottimizzazioni interne.

Basti prendere in esame il chip Fijitsu A64FX ovvero la CPU utilizzata nel supercomputer ARM più potente al mondo, Fugaku: ecco, anch’esso decodifica le istruzioni ARM in più micro-ops.

ARM64 e x86-64: entrambe sentono il peso degli anni

Jim Keller, nell’intervista che abbiamo citato in apertura, ha fatto notare che sia x86-64 che ARM64 risultano appesantite dalle caratteristiche legacy, superate dopo anni di continui miglioramenti. Entrambe le architetture, ad esempio, hanno aggiunto funzionalità nel tempo man mano che le esigenze del software si evolvevano; allo stesso tempo sono state parzialmente ripulite di alcuni vecchi set di istruzioni proprio quando si è verificato il passaggio ai 64 bit. Anche nelle implementazioni moderne, però, permangono pesanti fardelli frutto di anni di evoluzioni: questo peso, spesso non più necessario, è divenuto tangibile tanto che ad esempio Intel sta guardando a un’architettura solo a 64 bit: x86S.

Lo storico ingegnere di Apple, AMD e Tesla, che di recente ha dato vita al progetto Atomic Semi con lo youtuber Sam Zeloof, ha dichiarato che RISC-V non deve confrontarsi con alcun pesante fardello in quanto non ha alcuna “eredità” da gestire: l’architettura si trova di fatto all’inizio del suo ciclo di vita e non vi è stata aggiunta inutile complessità. “Se voglio costruire un computer molto velocemente oggi e desidero che sia performante, RISC-V è la scelta più ovvia. È l’architettura più semplice, ha tutte le funzionalità giuste, ha le prime otto istruzioni sulle quali devono concentrarsi delle ottimizzazioni“, ha aggiunto Keller.

In conclusione, la sfida lanciata da ARM a Intel in molteplici segmenti di mercato è davvero interessante. Chi sceglie ARM, tuttavia, non ottiene un vantaggio competitivo in forza del set di istruzioni utilizzato: per vincere, i produttori di chip ARM devono necessariamente fare affidamento sull’abilità dei loro team di progettazione. Oppure, possono superare in astuzia Intel e AMD ottimizzando i chip ARM per specifici obiettivi di potenza e prestazioni. Quanto fatto con Apple Silicon dalla Mela ne è l’esempio lampante: la storia di Apple e della nascita del chip M1 per Mac è il frutto di pesanti e costose attività di ricerca e sviluppo iniziate anni prima del lancio sul mercato.

/https://www.ilsoftware.it/app/uploads/2023/05/x86-64-ARM64-ISA.jpg)

/https://www.ilsoftware.it/app/uploads/2025/04/Chip-AMD-EPYC-Venice.jpg)

/https://www.ilsoftware.it/app/uploads/2025/04/amd-epyc-9005-turin-ubuntu-linux-prestazioni.jpg)

/https://www.ilsoftware.it/app/uploads/2025/04/chip-tenstorrent-blackhole.jpg)

/https://www.ilsoftware.it/app/uploads/2025/04/accordo-intel-tsmc.jpg)