/https://www.ilsoftware.it/app/uploads/2023/05/img_24657.jpg)

All’inizio di quest’anno avevamo parlato del poderoso investimento TSMC da 20 miliardi per lo sviluppo dei nuovi chip basati su processi costruttivi avanzati.

Questa volta, infatti, è stata la società taiwanese a trovarsi in ritardo sulla tabella di marcia, in particolare rispetto all’utilizzo del nodo a 3 nm e del processo litografico a 2 nm GAAFET del quale si parlava da anni.

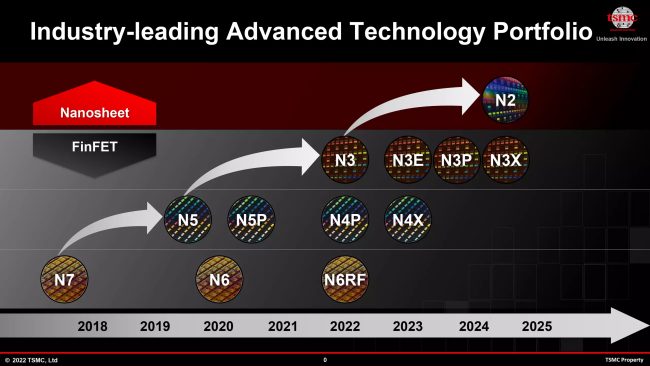

TSMC è adesso intervenuta per svelare la sua roadmap aggiornata almeno in parte. Per il processo a 3 nm (N3 nel gergo aziendale) la società manterrà la tecnologia FinFET con le “pinne” che sporgono dal corpo del transistor (terminali gate e drain).

Saranno però ben cinque i processi litografici N3 che TSMC metterà a disposizione dei suoi clienti: i primi due sono N3 e N3E (2022 e 2023); tre si aggiungeranno nel 2024 e useranno l’architettura FinFlex (“pinna flessibile”). Questi ultimi permetteranno infatti di variare le dimensioni del canale sulla base delle esigenze dei clienti.

A seconda della necessità di migliorare le prestazioni, la densità dei transistor o il consumo, i nuovi processi costruttivi FinFlex si chiameranno N3P, N3S e N3X.

Un approccio diverso da quello di Intel che, almeno con riferimento ai processi costruttivi più recenti, usa un’unica soluzione per tutte le possibili esigenze. E ciò nonostante l’azienda stia investendo per produrre chip x86, ARM e RISC-V per conto terzi.

Nel caso di TSMC, con N3 la società promette il 34% di consumi in meno rispetto a N5 a parità di frequenza, il 18% di prestazioni in più a parità di consumo, una riduzione dello spazio occupato da strutture logiche equivalenti tra i due processi del 37,5% con un aumento 60% nella densità dei transistor per millimetro quadrato. Alla fine la ricetta sarà basata su una combinazione di parametri decisa da ogni singolo partner.

TSMC rivela che FinFlex consentirà ai suoi clienti una personalizzazione molto più granulare dei chip in modo che essi possano soddisfare i requisiti di consumo-densità-potenza.

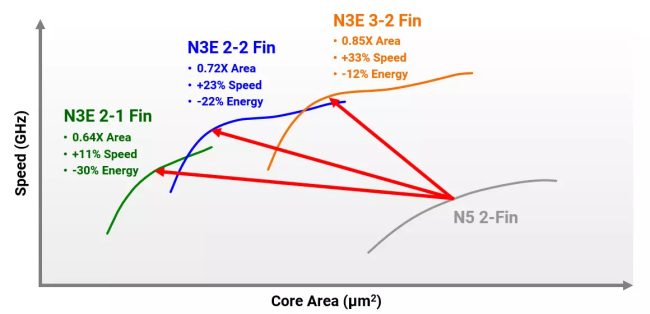

Se il cliente vuole il massimo delle prestazioni, con FinFlex potrà sfruttare strutture logiche con tre gate e due pinne per creare i chip che daranno fino al 33% in più in termini di frequenza di clock con un risparmio in termini di consumi energetici che non supera il 12% e il 15% in termini di area occupata.

Se viceversa si vogliono ridurre al minimo i consumi energetici, TSMC è pronta a realizzare i chip con transistor a due porte e una pinna. In questo modo i consumi si riducono del 30%, l’area occupata è inferiore del 36% a fronte di un +11% di performance. Il tutto prendendo come metro di paragone il processo a 5 nm della stessa azienda.

A differenza dei precedenti processi litografici, inoltre, le strutture di ciascuna combinazione di transistor possono essere mescolate all’interno dello stesso blocco. Ad esempio, una struttura 3-2 può essere utilizzata per la CPU ad alte prestazioni e una 2-1 per implementare una GPU a basso consumo energetico. L’obiettivo è evidentemente quello di assicurare grande flessibilità in termini di progettazione.

Il processo litografico TSMC a 2 nm: l’azienda punta su GAAFET

Della tecnologia GAAFET o a Nanosheet abbiamo già avuto modo di parlare in passato.

Nei transistor GAAFET vengono utilizzati dei “nanocollegamenti” tra source e drain con il gate posto al di sotto del canale, non soltanto nelle parti superiore e laterali. In questo modo è possibile impilare verticalmente le estremità del transistor anziché solo di lato: da qui il termine Nanosheet per la somiglianza dello schema con le pagine di un libro poste l’una sopra l’altra.

Uno dei primi vantaggi che la soluzione GAAFET introduce risiede nella minore energia necessaria per far funzionare i transistor.

Rispetto a N3E, il processo N2 a 2 nm, atteso per il 2024 con un avvio della produzione di massa nel 2025, sarà contraddistinto dal 30% in meno di consumo alla stessa frequenza o fino al 15% in più di prestazioni a parità di consumo. Dati simili a quelli che caratterizzano il passaggio da N5 a N3. In termini di densità, invece, il balzo in avanti sarebbe molto contenuto (+10%).

Controllando la larghezza dei Nanosheet sarà possibile aumentare la potenza del chip lavorando sulle dimensioni. Una variabile che si presterà alla realizzazione di molteplici versioni di chip, anche molto diversi l’uno dall’altro.

/https://www.ilsoftware.it/app/uploads/2025/04/SoC-intel-automotive.jpg)

/https://www.ilsoftware.it/app/uploads/2025/04/intel-18a-dettagli-tecnici.jpg)

/https://www.ilsoftware.it/app/uploads/2025/04/Chip-AMD-EPYC-Venice.jpg)

/https://www.ilsoftware.it/app/uploads/2025/04/amd-epyc-9005-turin-ubuntu-linux-prestazioni.jpg)